Your **definitive** source for quality pre-owned equipment.

## **Artisan Technology Group**

(217) 352-9330 | sales@artisantg.com | artisantg.com

#### Full-service, independent repair center

with experienced engineers and technicians on staff.

We buy your excess, underutilized, and idle equipment along with credit for buybacks and trade-ins.

#### **Custom engineering**

so your equipment works exactly as you specify.

- Critical and expedited services

- Leasing / Rentals / Demos

In stock / Ready-to-ship

ITAR-certified secure asset solutions

Expert team | Trust guarantee | 100% satisfaction

All trademarks, brand names, and brands appearing herein are the property of their respective owners.

Find the Abaco Systems / SBS ABI-PC2 at our website: Click HERE

# 1553 ADVANCED BUS INTERFACE FOR PC (ABI-PC2)

# REFERENCE MANUAL

Microcode Load for ABI Function

Microcode Product Number: 0118

Microcode Version:

Microcode Loads for PASS-1000 Function

Microcode Product Number: 0903

Microcode Version:

Microcode Product Number: 0904 Microcode Version:

August 15, 1994

Document Number ABI-PC2-94227

# **ERRATA**

This section details corrections to the following documents:

ABI-PC2 Reference Manual, January 18, 1995 (see cover page for current date)

ABI-V3 Reference Manual, August 15, 1994

ABI-Q Reference Manual, August 15, 1994

ABI-V2 Reference Manual, August 15, 1994

ABI-PC/AT Reference Manual, August 15, 1994

ABI-V4 Reference Manual, December 15, 1995

## **ALL DOCUMENTS**

## **Built-In Test Routines**

The procedure for BIT #3 should read as follows:

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "3". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offset 0040h with "0000".

- 5. Start ABI by loading offset 0000h with "0240" followed by loading offset 0000h with "0242". NOTE: If running this test on a PASS-1000, load offset 0000h with "0040", followed by "0042".

- 6. Load starting test address in offset 0044h. Minimum acceptable value is "0080".

- 7. Load ending test address in offset 0045h. Maximum acceptable value is "FFFF".

- 8. Start the test by writing "0001" to the Command (CMD) word at offset 0040h.

- 9. Wait for offset 0040h to equal "0000".

- 10. Check offset 0043h. If a nonzero value is present at this offset, errors occurred during the test.

## **ABI Operations Overview**

#### **Error Table**

Add error code 15E to this table. This error occurs when an RT sends an extra data word.

## **ABI-PC2 & ABI-V3 ONLY**

The information contained in the following paragraphs applies <u>only</u> to products having the following microcode loads:

ABI-V3 M019H and above ABI-PC2 M025E and above

The microcode load is listed on the product box label and is also printed on the labels attached to the actual PROMs on the board. If you are unable to determine the microcode load for your SBS product, contact SBS Technologies at 1-800-SBS-1553 or (505) 875-0600.

### **Built-In Test Routines**

## Microcode Organization, second paragraph, page 3-1

For products having the microcode loads listed above, the Built-In-Test (BIT) microcode is found only in the high PROM area. Select a specific BIT routine by calling one of seven starting addresses, listed in Table 3-1.

| Table 3-1 BIT Addresses               |                   |                                                         |  |  |

|---------------------------------------|-------------------|---------------------------------------------------------|--|--|

| Microprogram Program Selected Address |                   | Description                                             |  |  |

| 0001h                                 | Built-In-Test # 1 | Tests Internal registers and addressing modes           |  |  |

| 0002h                                 | Built-In-Test #2  | Tests ALU and condition code operation                  |  |  |

| 0003h                                 | Built-In-Test #3  | Tests RAM with Read/Write/Verify pattern-specific data  |  |  |

| 0004h                                 | Built-In-Test #4  | More testing of internal registers and addressing modes |  |  |

| 0005h                                 | Built-In-Test #5  | Tests on-board timer sub-system                         |  |  |

| 0006h                                 | Built-In-Test #6  | Tests 1553 interface logic and front end                |  |  |

| 0007h                                 | Built-In-Test #7  | Tests external discrete trigger function                |  |  |

## Built-In Tests 1-7, pages 3-3 through 3-12

Each BIT test includes a "Start" instruction which involves loading offset 0000h with either "0242" or "0042." For products having the microcode loads listed above, load offset 0000h with "0242."

## **Full Function Programmer's Reference**

#### **Microcode Initialization, page 4-19**

When an ABI module is powered-up or reset, the host software must perform the proper startup procedure to initialize the microcode program.

|          | Table 4-6 Microcode Program Identification |                     |                                                                      |  |  |

|----------|--------------------------------------------|---------------------|----------------------------------------------------------------------|--|--|

| Micropro | Microprogram ID # Microprogram Description |                     | Where Discussed                                                      |  |  |

| 1        | 0001h                                      | Reserved            |                                                                      |  |  |

| 2        | 0002h                                      | Reserved            |                                                                      |  |  |

| 3        | 0003h                                      | Reserved            |                                                                      |  |  |

| 4        | 0004h                                      | Reserved            |                                                                      |  |  |

| 5        | 0005h                                      | Reserved            |                                                                      |  |  |

| 6        | 0006h                                      | Reserved            |                                                                      |  |  |

| 7        | 0007h                                      | Reserved            |                                                                      |  |  |

| 8        | 0008h                                      | Reserved            |                                                                      |  |  |

| 9        | 0009h                                      | Reserved            |                                                                      |  |  |

| 10       | 000Ah                                      | Reserved            |                                                                      |  |  |

| 11       | 000Bh                                      | Reserved            |                                                                      |  |  |

| 12       | 000Ch                                      | Reserved            |                                                                      |  |  |

| 13       | 000Dh                                      | Full Function 1553B | "1553 Microcode Program Startup Procedure" in this manual subsection |  |  |

| 14       | 000Eh                                      | Reserved            |                                                                      |  |  |

| 15       | 000Fh                                      | Reserved            |                                                                      |  |  |

The Application Main Body program is the entry point for the "Full Function 1553B" microcode program that executes the BC, RT, Monitor, and Interrupt functions of this interface.

For products having the microcode loads listed above, the Built-In-Test routines are contained in the upper half of the PROM and application microcode in the lower half. To run the application microcode, select the lower PROM area (set CSR bit 9 to "0") in the "1553 Microcode Program Startup Procedure" which follows in this subsection.

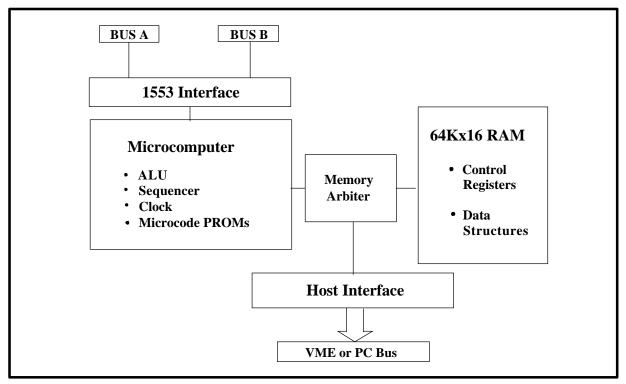

# INTRODUCTION

The Advanced Bus Interface (ABI) is a single card, real-time MIL-STD-1553 interface module for PC and VME host systems. The ABI provides the host system an advanced 1553 interface, including the following features: simultaneous and independent simulation of Bus Controller and 31 Remote Terminals, real-time monitoring, double-buffered monitoring and flexible event Interrupt capabilities. The ABI may be configured for one or more of these functions.

This manual provides detailed information on ABI setup and operations and is organized according to the following table (continued on following page).

| Table 1-1 ABI Manual Organization |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Section                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Introduction                      | Provides a description of the Reference Manual organization, and a discussion of the relationship between the Reference Manual and Interface Libraries Manual.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Hardware Installation             | This section describes the steps required to install the ABI into the host system. For VME systems, the proper system address, interrupt level and interrupt vector must be set on the ABI board. The user may also set hardware jumpers to configure ABI system clock sources (internal ABI clock or external clock source). Switch and jumper settings are explained in this section.  There is also a general discussion on configuring the ABI for short stub (1553A typically) or long stub (1553B) configurations, and the proper physical connections of the ABI to a 1553 bus. |  |  |

| Built-In-Test Routines            | This section describes the various ABI Built-In-Test (BIT) routines that provide a comprehensive diagnostic utility for the ABI. Each test description explains the functionality, execution procedure and expected results for the BIT.                                                                                                                                                                                                                                                                                                                                               |  |  |

| Table 1-1 ABI Manual Organization       |                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Section                                 | Description                                                                                                                                                                                                                                                                                                                   |  |  |

| Full Function<br>Programmer's Reference | This section provides a detailed overview of the ABI architecture and operations. The section includes an introduction and five subsections as described below:                                                                                                                                                               |  |  |

|                                         | <b>Introduction/ABI Operations Overview</b> - Provides a general system description and details the memory organization of the ABI.                                                                                                                                                                                           |  |  |

|                                         | <b>Microcode Init</b> - Explains the procedure the host computer must follow to properly initialize ABI operations.                                                                                                                                                                                                           |  |  |

|                                         | <b>BC Simulation -</b> Describes the ABI Bus Controller functions and the related data structures.                                                                                                                                                                                                                            |  |  |

|                                         | <b>RT Simulation -</b> Describes the ABI Remote Terminal functions and the related data structures.                                                                                                                                                                                                                           |  |  |

|                                         | <b>Bus Monitoring</b> - Describes the two types of 1553 bus monitoring available with the ABI (Sequential and Map Monitoring) and the related data structures. The data structures used for Map Monitoring overlap those used for RT Simulation; therefore, both subsections must be read to fully understand Map Monitoring. |  |  |

|                                         | <b>Interrupts</b> - Describes the action taken by the host to cause an ABI interrupt. This subsection also details the proper procedure for servicing both hardware and software polling interrupts.                                                                                                                          |  |  |

Most of the procedures described in the *BIT Routines* section and *Full Function Programmer's Reference* section for setting-up and running ABI 1553 functions are provided as C functions or Ada procedures in the Interface Libraries. For example, the "1553 Microcode Program Startup Procedure" described in the *Full Function Programmer's Reference* can be performed by host software through one of two C function calls: "init\_device()" or "start\_microcode()". There are many defined library functions provided to simplify the host integration effort.

ABI users should first read the *Full Function Programmer's Reference* section, followed by the Interface Libraries Manual.

# ABI-PC2 Hardware Installation TABLE OF CONTENTS

| Introduction                                                |

|-------------------------------------------------------------|

| Operational and Storage Specifications                      |

| Front Panel Connectors                                      |

| Unpacking and Inspecting the Equipment                      |

| Setting the ABI-PC2 RAM Base Address in PC Memory Space     |

| Setting the ABI-PC2 Base Address                            |

| Setting the ABI-PC2 <u>I/O</u> Base Address in PC I/O Space |

| Monitor Daughter Board                                      |

| Setting the ABI-PC2 Interrupt Level                         |

| External Connector Pinouts                                  |

| Installing the ABI-PC2 into a PC/AT System                  |

| PASS-1000 Installation                                      |

| Connecting the ABI to a 1553 Bus                            |

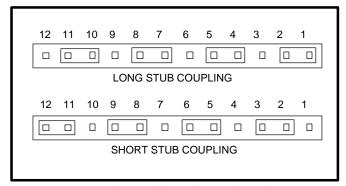

| Selecting Long or Short Stub Connection Circuitry 2-1       |

| Power Application                                           |

| Testing the Board                                           |

| Variable Voltage Control of the 1553 Bus Waveforms          |

# **ABI-PC2 Hardware Installation TABLE OF FIGURES AND TABLES**

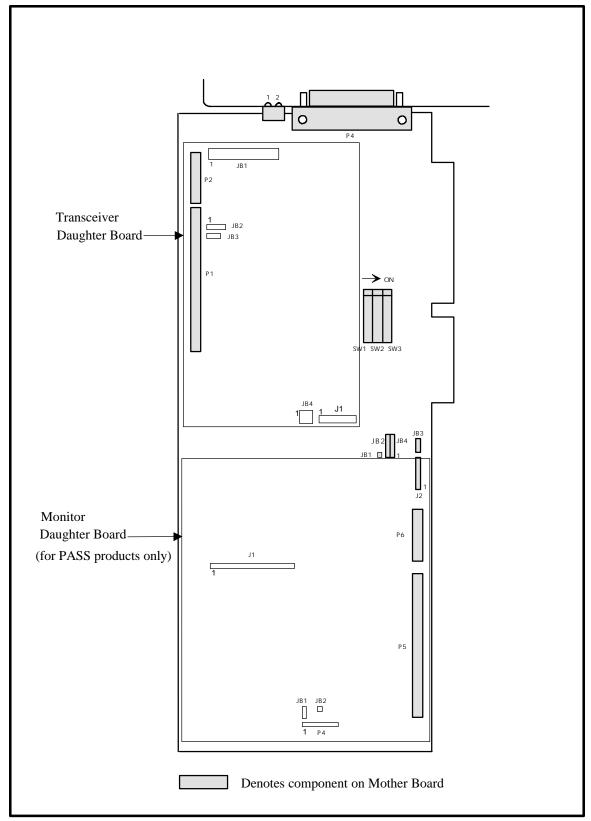

| Figure 2-1 ABI-PC2 Board Layout                           |

|-----------------------------------------------------------|

| Table 2-1 PC/AT Memory Map                                |

| Figure 2-2 Default Base Address Switch Positions          |

| Table 2-2 Default Base Address Selection                  |

| Figure 2-3 Switch Positions for Base Address in DOS Space |

| Table 2-3 Base Address in DOS Space                       |

| Figure 2-4 Default I/O Base Address Switch Positions      |

| Table 2-4 I/O Base Address Selection                      |

| Figure 2-5 Example of ABI-PC2 Interrupt Level 15          |

| Table 2-5 Interrupt Level Selection                       |

| Table 2-6 Connector P4 Pinout                             |

| Figure 2-6a Incorrect Method of Bus Coupling (Long Stubs) |

| Figure 2-6b Correct Method of Bus Coupling (Long Stubs)   |

| Figure 2-7 Bus Coupling (Short Stubs)                     |

| Figure 2-8 Long or Short Stub Selection with JB7 and JB8  |

| Table 2-7 Control Register Bit Definitions                |

| Table 2-8 Variable Voltage Output Selection               |

## ABI-PC2 HARDWARE INSTALLATION

## Introduction

The ABI-PC2 is a single-board MIL-STD-1553 interface for an IBM PC/AT, or IBM compatible computer system. This section describes the unpacking, configuration, and installation of an ABI-PC2 into a host computer. Because proper installation is critical to the successful operation of the ABI-PC2, SBS Engineering recommends that the steps described here be followed explicitly. The steps involved in the installation include:

- Unpacking and Inspecting the Equipment

- Setting the ABI-PC2 RAM Base Address in PC Memory Space

- Setting the ABI-PC2 I/O Base Address in PC I/O Space

- Setting the ABI-PC2 Interrupt Level

- Selecting Long or Short Stub Connection

- Installing the Configured Board into the PC System

- Testing the Installed Board

Note: This is an electronic product that is sensitive to electrostatic discharge. Normal precautions should be observed in handling the board to prevent damage.

## **Operational and Storage Specifications**

- Maximum Power Consumption:

- 5 volts at 2.5 amps

Front Donal Connectors

- 12 volts at 400 milliamps

- Operating Temperature: 0° to 70° Celsius, at less than or equal to 95% humidity

- Storage Temperature: -65° to 150° Celsius, at less than or equal to 95% humidity

- Shock requirements are to the highest commercial standards

- Mean Time Between Failures: 72,000 hours, based on MIL-HDBK-217F

## **Front Panel Connectors**

| From Faner Connectors |          |             |              | Mating Connect | UIS                 |                    |

|-----------------------|----------|-------------|--------------|----------------|---------------------|--------------------|

|                       | Location | Part Number | Manufacturer | Pigtails       | Part Number         | Manufacturer       |

|                       | P4       | CA2047      | Milestek     | Bus A & B      | PL75                | Trompeter          |

|                       |          |             |              | trigger, IRIG  | mating connector of | lependent on cable |

SBS sells bus configurations, part numbers BUS-2 (2-stub coupler) and BUS-3 (3-stub coupler), for transformer coupled systems. Contact SBS at 505-345-5353 for more information.

Moting Connectors

#### ABI-PC2 Hardware Installation

Other components are available from: MilesTek

1 Lake Trail Drive Argyle, Texas 76226

Attn: Frank or Jeanette Miles

800-524-7444 800-683-7444

MilesTek also provides the following:

twin-axial cable CA2009-xxx (xxx denotes length)

1553 bus terminator 10-06403-025

# **Unpacking and Inspecting the Equipment**

The ABI is shipped in a single box that contains the ABI board, cable adapter, and this manual. Carefully unpack the board and inspect it for any visible damage that could have occurred during shipment. If there is visible damage, contact SBS Engineering. When calling SBS, have the board and board serial number available.

Figure 2-1 ABI-PC2 Board Layout

## **Setting the ABI-PC2 RAM Base Address in PC Memory Space**

The ABI-PC2 contains 128 kilobytes (64 kilowords) of on-board RAM. This RAM may either be configured as one 128 kilobyte block or as two overlayed 64 kilobyte blocks at the same address. The base address of the board can be assigned any address that is on a 128 kilobyte boundary. Before setting the base address, study the unused memory blocks in the host system to determine if the board should be configured with a block of length 128 or 64 kilobytes.

The memory map of a PC-AT consists of the DOS memory area and the Extended memory area. If the ABI-PC2 is mapped into the DOS area, the board can be accessed using readily available software compilers. The drawback to mapping the board into the DOS area is that the amount of unused memory space is limited. The drawback to using the extended area is that the board can only be accessed using extended memory device drivers or compilers that run in 32-bit protected mode. If the ABI is mapped into this area and the user wishes to use a standard compiler, a device driver must be used to access the board. The use of a device driver causes each access of the board to be considerably slower than if the board is mapped into the DOS area or if a 32-bit protected mode compiler is used.

The DOS memory area consists of the addresses from 000000h to 100000h. Within this area, certain addresses are reserved by DOS and must not be used by the ABI-PC2. Use the DOS DEBUG program to read the memory block and determine if it is unused. (If all of the data in the block is FFh, the block is probably unused.) Typical good DOS addresses for the ABI-PC2 are 0D0000h and 0E0000h.

The Extended memory area consists of the addresses from 100000h to FFFFFFh. The ABI-PC2 may be installed at any address within this range, as long as it is **above the RAM configuration of the machine**. Therefore, if the extended RAM area of the PC system is full, typically 32 megabytes, the upper 16 megabytes must be removed prior to mapping the ABI-PC2 in extended memory.

The decision of where to map the ABI is up to the user and should be determined based on the memory spaces available, the type of compiler to be used, and the speed needed for the application. The factory default base address for the ABI-PC2 is F00000h, in extended memory.

Table 2-1 contains the memory map of the PC/AT, and should be used to help determine a possible base address for the ABI-PC2.

| Table 2-1 PC/AT Memory Map |            |                                                                                                                                                                                         |  |  |

|----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Address Range              | Length     | Description                                                                                                                                                                             |  |  |

| 000000h - 0BFFFFh          | 768K Bytes | Reserved for DOS.                                                                                                                                                                       |  |  |

| 0C0000h - 0CFFFFh          | 64K Bytes  | Unused. May be used by video adaptors.                                                                                                                                                  |  |  |

| 0D0000h - 0DFFFFh          | 64K Bytes  | Unused. This block may be used by certain adaptors or by an Expanded Memory Manager (EMM). This block car only be a base address if the board is configured in the 64K byte block mode. |  |  |

| 0E0000h - 0EFFFFh          | 64K Bytes  | DOS ROM area. May be unused in an IBM compatible computer.                                                                                                                              |  |  |

| 0F0000h - 0FFFFFh          | 64K Bytes  | DOS ROM area.                                                                                                                                                                           |  |  |

| 100000h - FFFFFFh          | 15M Bytes  | s Extended Memory area. Some or all of this area may be used by extended memory installed in the system.                                                                                |  |  |

## **Setting the ABI-PC2 Base Address**

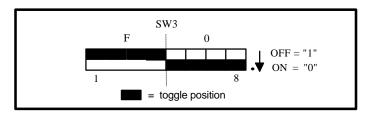

Switch SW3 is used to select the base address of the ABI-PC2. If the desired value of the address line is "0", the switch should be placed in the ON position; if the desired value is "1", the switch should be placed in the OFF position. Figure 2-2 illustrates the switch positions for the factory default base address (F00000h). The switch is read from left to right with SW3-8 being the least significant position. Table 2-2 shows the relationship between the switch positions and the address lines as well as an example of the default base address setting. Note: Bits 0 through 15 are not selectable and default to zeros.

Figure 2-2 Default Base Address Switch Positions

| Table 2-2 Default Base Address Selection |        |               |                |  |

|------------------------------------------|--------|---------------|----------------|--|

| Address Bit                              | Switch | Desired Value | Switch Setting |  |

| A23                                      | SW3-1  | 1             | OFF            |  |

| A22                                      | SW3-2  | 1             | OFF            |  |

| A21                                      | SW3-3  | 1             | OFF            |  |

| A20                                      | SW3-4  | 1             | OFF            |  |

| A19                                      | SW3-5  | 0             | ON             |  |

| A18                                      | SW3-6  | 0             | ON             |  |

| A17                                      | SW3-7  | 0             | ON             |  |

| A16                                      | SW3-8  | 0             | ON             |  |

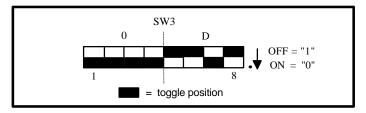

Figure 2-3 and Table 2-3 show the switch positions for the DOS memory base address 0D0000h.

Figure 2-3 Switch Positions for Base Address in DOS Space

| Table 2-3 Base Address in DOS Space |        |                  |                   |  |

|-------------------------------------|--------|------------------|-------------------|--|

| Address Bit                         | Switch | Desired<br>Value | Switch<br>Setting |  |

| A23                                 | SW3-1  | 0                | ON                |  |

| A22                                 | SW3-2  | 0                | ON                |  |

| A21                                 | SW3-3  | 0                | ON                |  |

| A20                                 | SW3-4  | 0                | ON                |  |

| A19                                 | SW3-5  | 1                | OFF               |  |

| A18                                 | SW3-6  | 1                | OFF               |  |

| A17                                 | SW3-7  | 0                | ON                |  |

| A16                                 | SW3-8  | 1                | OFF               |  |

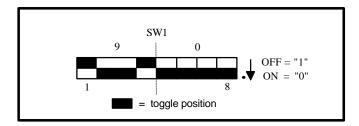

## Setting the ABI-PC2 **I/O** Base Address in PC I/O Space

Switch SW1 is used to set the base I/O address of the ABI Control Register. The Control Register is used to control the following:

- Enabling the ABI-PC2

- Selecting between 128K Byte and 64K Byte Modes

- Selecting between upper or lower blocks (64K Byte mode only)

The I/O base address of the Control Register can be set to any value between 300h and 3FFh. The eight switches of SW1 correspond to the eight least significant address lines. Table 2-4 shows the correspondence between the switches and the address lines, along with an example for the default setting of 390h.

Figure 2-4 Default I/O Base Address Switch Positions

| Table 2-4 I/O Base Address Selection |        |                  |                   |  |

|--------------------------------------|--------|------------------|-------------------|--|

| Address Bit                          | Switch | Desired<br>Value | Switch<br>Setting |  |

| A7                                   | SW1-1  | 1                | OFF               |  |

| A6                                   | SW1-2  | 0                | ON                |  |

| A5                                   | SW1-3  | 0                | ON                |  |

| A4                                   | SW1-4  | 1                | OFF               |  |

| A3                                   | SW1-5  | 0                | ON                |  |

| A2                                   | SW1-6  | 0                | ON                |  |

| A1                                   | SW1-7  | 0                | ON                |  |

| A0                                   | SW1-8  | 0                | ON                |  |

## **Monitor Daughter Board**

When the Monitor Daughter Board is installed (for use with PASS products), it takes up extra I/O address space. If installed in extended memory, it uses 128 kilobytes of address space immediately following the base address and I/O base address.

# **Setting the ABI-PC2 Interrupt Level**

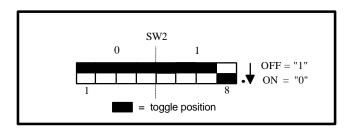

Switch SW2 is used to set the interrupt level used by the ABI-PC2. The user can choose between eight different interrupt levels or no interrupts. Table 2-5 contains a list of the possible interrupt level settings along with their use in an IBM PC/AT system. Only one of the switch positions in SW2 can be ON; if more are ON, undetermined results will occur. Also, if an interrupt level is selected that is used by another device, undetermined results will occur.

Figure 2-5 Example of ABI-PC2 Interrupt Level 15

| Table 2-5 Interrupt Level Selection |                    |                             |  |

|-------------------------------------|--------------------|-----------------------------|--|

| Switch<br>(SW2)                     | Interrupt<br>Level | Use in PC/AT                |  |

| ALL OFF                             | NONE               |                             |  |

| SW2-1                               | IRQ3               | COM2. Second serial port.   |  |

| SW2-2                               | IRQ5               | LPT2. Second parallel port. |  |

| SW2-3                               | IRQ7               | LPT1. First parallel port.  |  |

| SW2-4                               | IRQ9               | Unused.                     |  |

| SW2-5                               | IRQ10              | Unused.                     |  |

| SW2-6                               | IRQ11              | Unused.                     |  |

| SW2-7                               | IRQ12              | Unused.                     |  |

| SW2-8                               | IRQ15              | Unused.                     |  |

## **External Connector Pinouts**

Table 2-6 shows the pinouts for the external ABI-PC2 connector labeled P4.

|     | Table 2-6 Connector P4 Pinout |     |                 |  |

|-----|-------------------------------|-----|-----------------|--|

| Pin | Signal                        | Pin | Signal          |  |

| 1   | Primary Bus +                 | 14  | Primary Bus -   |  |

| 2   | Secondary Bus +               | 15  | Secondary Bus - |  |

| 3   | Reserved                      | 16  | Reserved        |  |

| 4   | Reserved                      | 17  | Reserved        |  |

| 5   | Reserved                      | 18  | Reserved        |  |

| 6   | Reserved                      | 19  | Reserved        |  |

| 7   | External Trigger *            | 20  | GND             |  |

| 8   | +5VDC                         | 21  | GND             |  |

| 9   | External Clock                | 22  | GND             |  |

| 10  | External Enable *             | 23  | GND             |  |

| 11  | External Clear *              | 24  | GND             |  |

| 12  | Reserved                      | 25  | GND             |  |

| 13  | +5VDC                         |     |                 |  |

|     | * active low signal           |     |                 |  |

# Installing the ABI-PC2 into a PC/AT System

The next step is to install the ABI into the desired slot in the host system. To do this, follow the instructions supplied by the system manufacturer.

### **PASS-1000 Installation**

If installing the ABI-PC2 for use with the PASS-1000, please refer to the "Installation" section of the PASS-1000 Reference Manual for software installation instructions.

## Connecting the ABI to a 1553 Bus

For operation, the ABI must be connected to a MIL-STD-1553 bus. This is not necessary for initial testing of the board. For test purposes, it is sufficient to simply connect standard bus terminators to the A and B bus connectors on the front panel of the interface.

These MIL-STD-1553 bus connections must be made very carefully. **The ABI will not operate properly if the bus connections are not correct.**

The MIL-STD-1553 bus consists of a twisted-pair cable with terminators at each end, ranging in length from a few inches to several hundred feet. The physical connection of a subsystem to this bus is called a stub. In MIL-STD-1553 there are two types of stubs defined: 1) long stubs or 2) short stubs. Short-stub connections to a bus are rarely used. Long-stub connections are the most common and require several components. These components include a transformer and two resistors, used at the exact point where the connection is made to the bus. These components are typically enclosed in a small module called a *bus coupler*. These couplers may provide for connection of only one stub or several stubs. The coupler has two connectors for the bus (usually at opposite ends of the coupler) and a connector for each stub (typically mounted perpendicular to the bus connectors).

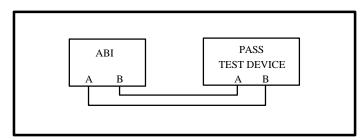

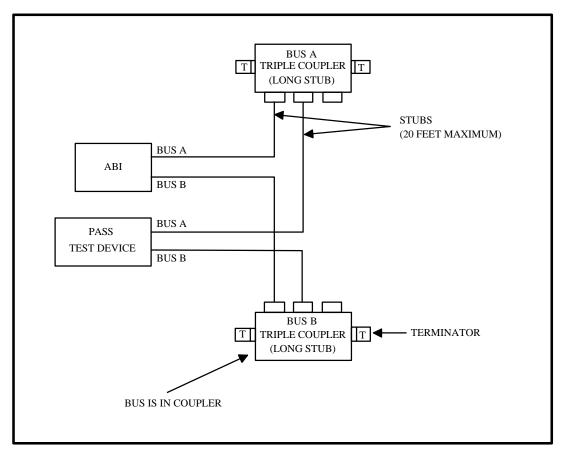

Subsystem stubs will not function properly if connected directly together. Proper coupling devices must be used for each stub and the bus must be properly terminated. Figures 2-6a and b illustrate the proper and improper connection schemes for long-stub coupling and the terminology used for the various components associated with the bus. A three-stub coupler is shown in the figure. In this case, the bus is contained entirely within the coupler. If other devices are to be connected to the bus, one of the terminators must be removed and replaced with a cable connecting this coupler to another coupler. The other coupler could then be terminated or the bus extended further.

Figure 2-6a <u>Incorrect</u> Method of Bus Coupling (Long Stubs)

Figure 2-6b Correct Method of Bus Coupling (Long Stubs)

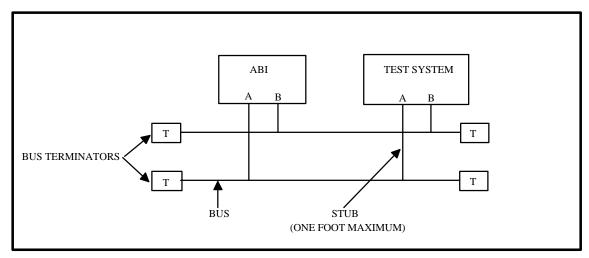

Figure 2-7 shows a short-stub connection. The <u>total</u> stub length must be less than one foot. Since this includes the length of the stub on the board, the actual stub should be less than nine inches. As previously mentioned, this method of coupling is rarely used.

Figure 2-7 Bus Coupling (Short Stubs) - NOT RECOMMENDED

## **Selecting Long or Short Stub Connection Circuitry**

The ABI can provide either a long or short stub interface to a MIL-STD-1553 bus. Jumper block JB1 on the Transceiver Daughter Board is used to select the proper interface circuitry on the board. The board is factory jumpered for long stub connections, which is by far the most common method used. If you are not sure which configuration is used with your system, set the board for long stub coupling. The jumpers used to make these selections are shown in Figure 2-8. If you wish to verify or change these jumpers, they should be set as shown in the figure.

Figure 2-8 Long or Short Stub Selection with JB7 and JB8

## **Power Application**

The next step is to power-up the computer system. Figure 2-1 shows two LEDs that are visible on the board's rear panel. These LEDs are labeled 1 and 2. LED 2 indicates proper initialization of the board at power-on time. LED 1 indicates that the board has been enabled using bit 0 of the I/O Control Register. At power-up, LED 2 should be illuminated and LED 1 should not be illuminated. If this is not the case, contact SBS Engineering.

## **Testing the Board**

Table 2-7 contains the bit definitions for the Control Register, a read/write eight-bit register. This register must be accessed, and bit 0 written to a "1" before the board can be accessed. When bit 0 is a "1", LED 1 will illuminate.

|                 | Table 2-7 Control Register Bit Definitions |                                                                                                                                                                                                                                      |  |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit<br>Position | Name                                       | Definition                                                                                                                                                                                                                           |  |

| 0               | Enable                                     | Board Enable. When written as a "1" the board is enabled. A "0" is used to disable the board. After power-up the board is disabled.                                                                                                  |  |

| 1               | Mode                                       | Block Size Mode. This bit selects between a 128K byte buffer length ("0"), and a 64K byte buffer length ("1").                                                                                                                       |  |

| 2               | Select                                     | Block Select. This bit is only valid when 64K byte block mode is selected. When this bit is a "0" the lower 64K bytes of ABI memory are selected for accessing. When this bit is "1" the upper 64K bytes of ABI memory are selected. |  |

When both LEDs are illuminated, the board can be accessed from the host at the address selected by the user during configuration. The user must determine a suitable method for accessing the board from software. The method used varies depending on the language used for programming.

Once the method has been determined, the user must write a program to test the board. SBS Engineering supplies a number of diagnostic and utility functions on the board in microcode which may be used to test the operation of the board. The section entitled "Built-In Test Routines" discusses a recommended procedure to be followed at this point to test the board. This test procedure should normally be included in a daily operational readiness user program.

## Variable Voltage Control of the 1553 Bus Waveforms

A voltage reference controls the peak-to-peak voltage level of the 1553 bus signals. The user can adjust this voltage reference by reprogramming a digital-to-analog converter (DAC). After power-up, the DAC is initialized to a setting for normal 1553 bus operation.

The DAC output value can be changed by writing a data value to the ABI at offset 1FBI at offset 1Fh. Each data bit has a final reference weighting of 50 millivolts. Normal 1553 bus operation occurs when a value of 00F0h is written to the DAC. Table 2-8 is included as reference only and, due to the loading of the bus, may vary from system to system.

| Table 2-8    | Varia | able Voltage Output Selection      |

|--------------|-------|------------------------------------|

| DAC<br>Value |       | 1553 Bus Voltage<br>(Peak to Peak) |

| 00F0         |       | 21.5                               |

| 00E0         |       | 20                                 |

| 00D0         |       | 19                                 |

| 00C0         |       | 17.5                               |

| 00B0         |       | 15.5                               |

| 00A0         |       | 14                                 |

| 90           |       | 12.5                               |

| 80           |       | 10.5                               |

| 70           |       | 9                                  |

| 60           |       | 7.5                                |

| 50           |       | 6.5                                |

| 40           |       | 4.5                                |

| 30           |       | 2.9                                |

| 20           |       | 1.1                                |

| 10           |       | 0.4                                |

| 0            |       | 0                                  |

# **BUILT-IN TEST ROUTINES**

#### Introduction

The ABI contains built-in-test capabilities which provide the user with an added level of hardware confidence and help to ease integration into new or existing systems. Many different routines are available to provide the user with information about various subsystems or devices on the ABI. This section describes each of these test routines, demonstrates how to execute them and explains how to interpret the results. Troubleshooting tips are also provided to assist in the initial integration and subsequent use of the board.

## **Microcode Organization**

The ABI microcode is stored in a set of five registered PROMs with a capacity of 8K bytes of microprogram data. The address bus for these PROMs is a 12-bit pipelined bus. An additional bit is used to select a high or low PROM area (See Table 4-2 in the "ABI Operations Overview" subsection of the *Full Function Programmer's Reference*). This **prom select** bit allows the microcode PROMs to store two separate and independent microprograms. When this bit is set to "0", the low PROM area is selected. When the thirteenth bit is set to "1", the high PROM area is selected.

Each PROM area (high and low) contains Built-In-Test (BIT) microcode followed by application microcode. The ABI may select a specific BIT routine or MIL-STD-1553 application microcode by calling one of 15 starting addresses. These microprogram starting addresses are listed in Table 3-1.

|                         | Table 3-1 BIT Addresses |                                                                                                    |  |  |

|-------------------------|-------------------------|----------------------------------------------------------------------------------------------------|--|--|

| Microprogram<br>Address | Program Selected        | Description                                                                                        |  |  |

| 0001h                   | Built-In-Test # 1       | Tests Internal registers and addressing modes.                                                     |  |  |

| 0002h                   | Built-In-Test # 2       | Tests ALU and condition code operation.                                                            |  |  |

| 0003h                   | Built-In-Test # 3       | Tests RAM with Read/Write/Verify pattern-specific data                                             |  |  |

| 0004h                   | Built-In-Test # 4       | More testing of internal registers and addressing modes.                                           |  |  |

| 0005h                   | Built-In-Test # 5       | Tests on-board timer sub-system.                                                                   |  |  |

| 0006h                   | Built-In-Test # 6       | Tests 1553 interface logic and front end.                                                          |  |  |

| 0007h                   | Built-In-Test # 7       | Tests external discrete trigger function                                                           |  |  |

| 000Dh                   | Application Code        | Starts application code. (See "Microcode Init" subsection of Full Function Programmer's Reference) |  |  |

The following pages show how to perform each BIT and how to interpret the results.

## **NOTE FOR ABI-PC2 USERS:**

Currently, the Built-in Test Routines included with the ABI-PC2 interface board are not all operational. Please note the following:

## ABI-PC2, Normal Configuration

Do not run BIT 7 or the "ALL BIT" test (which includes BIT 7). BIT 7 does not run properly and will result in a system "lock-up".

## ABI-PC2, PASS-1000 Configuration

Do not run BITs 5, 6, 7 or the "ALL BIT" test.

In addition, do not use the "RUN ALL BIT" test included with the Interface Libraries.

## **Executing the ABI Built-In-Tests**

Certain memory offsets must be loaded with specific values prior to executing a built-in test. Instructions for programming these locations are included with each test procedure.

## **BIT #1**

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "1". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offsets 0040h to 004Fh with "0".

- 5. Load offsets 0044h, 004Ch, and 004Eh with "FFFF".

- 6. Start ABI by loading offset 0000h with "0042". (Start )

BIT #1 is complete when offset 0040h has changed from "0" (after a few microseconds) to a non-zero value. Check the results against Table 3-2.

# **Results:**

|         | Table 3-2 BIT #1 Results |                                                                                             |  |  |

|---------|--------------------------|---------------------------------------------------------------------------------------------|--|--|

| Address | Expected Contents        | Description                                                                                 |  |  |

| 0040h   | non-zero value           | BIT Code version number. Exact number may vary, but should be similar to 0402.              |  |  |

| 0041h   | 0001                     | Base register 0, pipeline source okay                                                       |  |  |

| 0042h   | 0002                     | Base register 1, pipeline source okay                                                       |  |  |

| 0043h   | FFFF                     | Indirect register 0 , pipeline source okay                                                  |  |  |

| 0044h   | 0000                     | Indirect register 1, pipeline source okay                                                   |  |  |

| 0045h   | XXXX                     | Echo input. Value written here will also be written to location 46 when BIT 1 is executing. |  |  |

| 0046h   | (45)                     | Echoed value of contents of location 45.                                                    |  |  |

| 0048h   | XXXX                     | Counter pattern. Indicates microcode is operating. Will be different every time it is read. |  |  |

| 0049h   | 0001                     | Base register 0, ALU source okay                                                            |  |  |

| 004Ah   | 0002                     | Base register 1, ALU source okay                                                            |  |  |

| 004Bh   | FFFF                     | Indirect register 0, ALU source okay                                                        |  |  |

| 004Ch   | 0000                     | Indirect register 1, ALU source okay                                                        |  |  |

| 004Dh   | FFFF                     | Base register 0, ALU Instruction source okay                                                |  |  |

| 004Eh   | 0000                     | Base register 1, ALU Instruction source okay                                                |  |  |

| 004Fh   | non-zero value           | Revision number for entire diagnostic and utilites microcode. Exact number may vary.        |  |  |

## BIT # 2

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "2". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offset 0040h with "FFFF".

- 5. Start ABI by loading offset 0000h with "0042". (Start )

- 6. Wait four microseconds.

- 7. Check contents of offset 0040h.

#### **Results:**

The contents of offset 0040h should be "0". Any bits set to "1" indicate an error; these are explained in Table 3-3.

| Table 3-3 BIT #2 Errors |                                    |  |

|-------------------------|------------------------------------|--|

| BIT#                    | INDICATES                          |  |

| 1                       | Failure of ZERO Condition Code     |  |

| 2                       | Failure of NEGATE Condition Code   |  |

| 3                       | Failure of CARRY Condition Code    |  |

| 4                       | Failure of OVERFLOW Condition Code |  |

#### **BIT #3**

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "3". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offset 0040h with "FFFF".

- 5. Start ABI by loading offset 0000h with "0042". (Start )

- 6. Load **starting** test address in offset 0044h.

- 7. Load **ending** test address in offset 0045h.

- 8. Start the test by writing one of the following values to the Command (CMD) word at offset 0040h.

| <u>Value</u> | Result                                                                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------|

| "1"          | Start test and perform one time only from the starting address to the ending address.                                     |

| "2"          | Start test and perform continuously from the starting address to the ending address. Halt only if an error occurs.        |

| "3"          | Start test and perform continuously from the starting address to the ending address. Do not halt even if an error occurs. |

BIT #3 performs a series of READ/WRITE/VERIFY operations, beginning with the starting address and continuing to each subsequent address. There are three values, "0000", "FFFF" and DATA=ADDR, used for these operations. The operations are performed for a random number of address locations using one of these values (i.e. "0000"). The BIT test then uses another of these values (i.e. "FFFF") to test the next group of addresses. After a random number of addresses have been tested with the second value, the BIT test will begin using the third value for the operations. This test pattern continues through the ending address. If more than one cycle has been requested, the next pattern will be different from the previous. The address locations used by the BIT #3 microcode are listed in Table 3-4.

# **Results:**

| Table 3-4 BIT #3 Addresses |                                                                      |  |

|----------------------------|----------------------------------------------------------------------|--|

| Address                    | Description                                                          |  |

| 40                         | CMD - Command word, used to start test.                              |  |

| 41                         | RSP - Response word. Microcode copies the CMD word to this location. |  |

| 42                         | LCNT - Loop Count. Number of test loops completed.                   |  |

| 43                         | EADR - Error Address. Indicates address where R/W/Verify error.      |  |

| 44                         | LOW - Starting Address for test range.                               |  |

| 45                         | HI - Ending Address for test range.                                  |  |

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "4". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offsets 0040h through 0042h with "0000".

- 5. Start ABI by loading offset 0000h with "0042". (Start )

- 6. Wait for one second, or for offset 0040h = "FFFF".

## **Results:**

The information shown in Table 3-5 is provided by the microcode.

| Table 3-5 BIT#4 Results |          |                                            |

|-------------------------|----------|--------------------------------------------|

| Address                 | Contents | Description                                |

| 0040h                   | FFFF     | Indicates test completion.                 |

| 0041h                   | 0000     | No Errors.                                 |

| 0041h                   | 0001     | Failure during Base Register 0 Verify.     |

| 0041h                   | 0002     | Failure during Base Register 1 Verify.     |

| 0042h                   | xxxx     | Base register contents at time of failure. |

| 0043h                   | xxxx     | Desired value of data.                     |

| 0044h                   | xxxx     | Actual value of data.                      |

This test performs Base Register tests similar to those in BIT # 1.

## **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "5". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offsets 0040h through 0044h with "0000".

- 5. Start ABI by loading offset 0000h with "0042". (Start )

- 6. Wait for one second, or for offset 0040h = "FFFF".

## **Results:**

The information shown in Table 3-6 is provided by the microcode.

| Table 3-6 BIT #5 Results |          |                                 |

|--------------------------|----------|---------------------------------|

| Address                  | Contents | Description                     |

| 40                       | FFFF     | Indicates test completion.      |

| 41                       | 0000     | Error Code, 0000 = No Error.    |

| 11                       | 0001     | Timer Write/Read Failure.       |

| "                        | 0002     | Timer Count/Read Failure.       |

| "                        | 0003     | OVFL Discrete will not reset.   |

| "                        | 0004     | DOVFL Discrete will not reset.  |

| 11                       | 0005     | OVFL Discrete set prematurely.  |

| 11                       | 0006     | DOVFL Discrete set prematurely. |

| "                        | 0007     | OVFL does not set.              |

| "                        | 8000     | DOVFL does not set.             |

| 42                       | xxxx     | Desired Value of Data.          |

| 43                       | xxxx     | Actual value of Data.           |

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "6". (Set MAP)

- 3. Load offset 003Fh with any value.

- 4. Load offsets 0040h through 005Fh with "0000".

- 5. Load offset 001Fh with "00F0". (Set variable voltage control register.)

- 6. Start ABI by loading offset 0000h with "0042". (Start )

NOTE: This test must be performed on a **properly terminated** 1553 bus or with terminators installed directly on the front panel connectors. The ABI is intended to be connected to the 1553 bus via a data bus coupler if long stub operation is selected. There must be no extraneous activity on the bus while BIT # 6 is being performed. If BIT #6 fails while the ABI is connected to the 1553 bus: disconnect the ABI from the bus, install terminators directly onto the board and perform the test again.

#### **Results:**

The information shown in Table 3-7 is provided by the microcode.

| Table 3-7 BIT #6 Addresses |          |                                 |  |

|----------------------------|----------|---------------------------------|--|

| Address                    | Contents | Description                     |  |

| 0040h                      | CMD      | Command Word. Should be "0000". |  |

| 0041h                      | LPC      | Loop count.                     |  |

| 0042h                      | ERC      | Error counter.                  |  |

| 0043h                      | TNM      | Test number of failure.         |  |

| 0044h                      | ERR      | Error number.                   |  |

If the bus is properly terminated and BIT #6 fails, note the TNM and ERR values and contact SBS Engineering. These values are defined in Tables 3-8 and 3-9.

| Table 3-8 TNM Values |                                                                  |  |

|----------------------|------------------------------------------------------------------|--|

| TNM Value (in hex)   | Description                                                      |  |

| 0010                 | Prime Bus Active (PBA)/Alternate Bus Active (ABA) Initial Check. |  |

| 0021                 | Serial Data Transmit/Receive Test.                               |  |

| 0022                 | Serial Data Transmit/Receive Test.                               |  |

| 0023                 | Serial Data Transmit/Receive Test.                               |  |

| 0024                 | Serial Data Transmit/Receive Test.                               |  |

| 0031                 | Gap Timer Test # 1.                                              |  |

| 0032                 | Gap Timer Test # 2.                                              |  |

| 0033                 | Gap Timer Test # 3.                                              |  |

| 0034                 | Gap Timer Test # 4.                                              |  |

| 0035                 | Gap Timer Test # 5.                                              |  |

| 0036                 | Gap Timer Test # 6.                                              |  |

| 0041                 | Data Lost Bit Test.                                              |  |

| 0042                 | Data Lost Bit Test                                               |  |

| Table 3-9 ERR Values |                                        |  |

|----------------------|----------------------------------------|--|

| ERR Value (in hex)   | Description                            |  |

| 0001                 | PBA = 1 > 20 Microseconds Error.       |  |

| 0002                 | ABA = 1 Error.                         |  |

| 0003                 | Remote Terminal/Subaddress Data Error. |  |

| 0004                 | Data Error.                            |  |

| 0005                 | Invalid Word Error.                    |  |

| 0006                 | Sync Type Error.                       |  |

| 0007                 | Gap Too Short Error.                   |  |

| 0008                 | Gap Too Long Error.                    |  |

| 0009                 | Gap Static Data Error.                 |  |

| 000A                 | Gap Counter Data Error.                |  |

| 000B                 | Lost Not Set Error.                    |  |

| 000C                 | Lost Set 1 Error.                      |  |

| 000D                 | Lost Set 2 Error.                      |  |

| 000E                 | PBA Time-out Error.                    |  |

| 000F                 | Data Ready (DRDY) Time-out Error.      |  |

| 0010                 | SARDY Time-out Error.                  |  |

| 0011                 | XRDY Time-out Error.                   |  |

#### **Procedure:**

- 1. Reset ABI by loading offset 0000h with "1". (Reset CSR)

- 2. Set MAP register by loading offset 0010h with "7". (Set MAP)

- 3. Load 003Fh with any value.

- 4. Load offsets 0040h through 0043h with "0000".

- 5. Start ABI by loading offset 0000h with "0042". (Start )

- 6. Load offset 0040h with a data value of "0001".

- 7. Verify that offset 0041h = "0001".

- 8. Repeat steps 5-7 using a data value of "0000".

- 9. Each time offset 0040h is loaded with "0000" or "0001", an echo of that value will appear at offset 0041. BIT #7 will continue to check registers 0040h and 0041h indefinitely until the ABI is reset. Steps 5-8 may be repeated while BIT # 7 is executing.

NOTE: This test must be performed with a jumper or shunt installed on the front panel between the Discrete Input and Discrete Output, pins P7-9 and P7-10. Refer to the *Hardware Installation* section for details on the location of these pins. This test has been included for future capabilities of the ABI. The discrete I/O functions are not used at this time. Execution of BIT 7 is optional and is left to the user's discretion.

# Full Function Programmer's Reference TABLE OF CONTENTS

| ABI Operations Overview                                 | 4-2  |

|---------------------------------------------------------|------|

| Addressing Considerations for Host Application Programs | 4-3  |

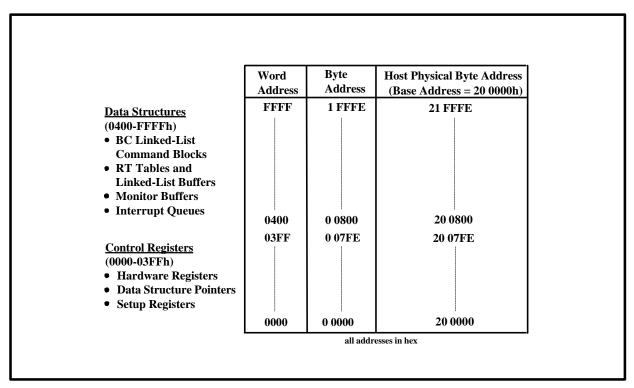

| ABI Memory Organization                                 | 4-4  |

| Data Structure Memory: 0400-FFFFh                       | 4-5  |

| Control Registers: 0000-03FFh                           | 4-5  |

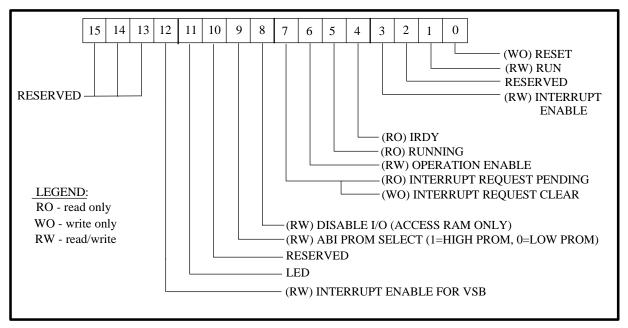

| Control Register Descriptions                           | 4-6  |

| Key Hardware Registers                                  | 4-10 |

| CSR (Control and Status Register)                       | 4-10 |

| MAP control register                                    | 4-12 |

| PSTEP control register                                  | 4-12 |

| System Clock Registers                                  | 4-12 |

| CCW (Clock Control Word), SCHIGH, SCLOW                 | 4-13 |

| Timing Hardware Registers                               | 4-13 |

| ITDRL, ITDRH (Internal Timer Data Registers)            | 4-13 |

| HDAT0 (Internal Timer Latch)                            | 4-14 |

| ITCR (Internal Timer Control Register), HDAT1           | 4-14 |

| Bit 0 - Clock Enable/Disable                            | 4-14 |

| Bit 1 - Clock Select                                    | 4-14 |

| Bit 2 - Reset Clock                                     | 4-14 |

| VVDR (Variable Voltage DAC Register)                    | 4-15 |

| Error Table                                             | 4-16 |

| Hardware Reset                                          | 4-18 |

| Microcode Initialization                                | 4-19 |

| ABI-PC2 Hardware Initialization                         | 4-20 |

| 1553 Microcode Program Startup Procedure                | 4-21 |

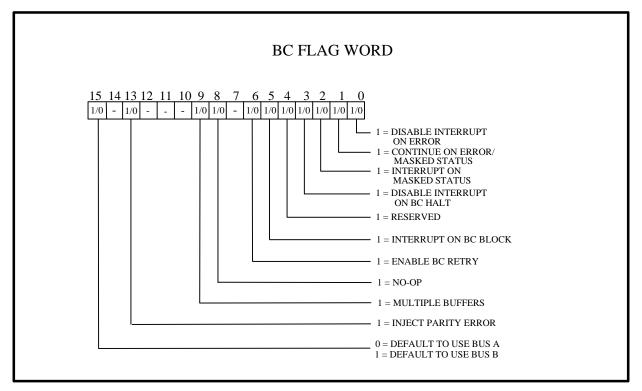

| Bus Controller Simulation                               | 4-23 |

| Control Block Structure                                 | 4-23 |

| Type                                                    | 4-24 |

| CMD 1                                                   | 4-24 |

| CMD 2                                                   | 4-25 |

| STS 1                                                   | 4-25 |

| STS 2                                                   | 4-25 |

|                                                         |      |

# Full Function Programmer's Reference TABLE OF CONTENTS

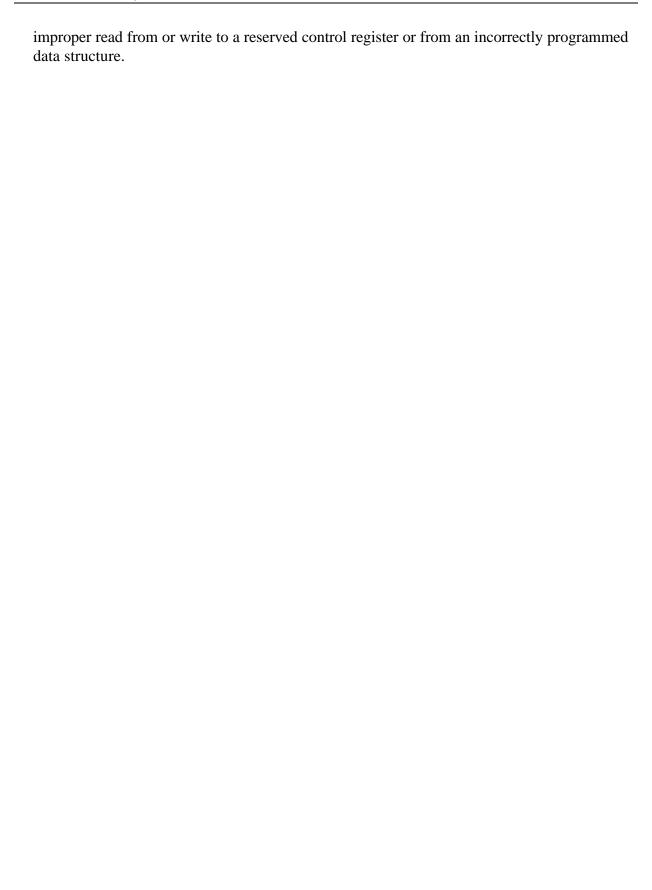

| FLAGS                                                               | 4-25 |

|---------------------------------------------------------------------|------|

| Bit 0 - Disable Interrupt on Error                                  | 4-25 |

| Bit 1 - Continue on Error                                           | 4-25 |

| Bit 2 - Interrupt on Masked Status                                  | 4-25 |

| Bit 3 - Disable Interrupt on Zero Link                              | 4-26 |

| Bit 6 - Enable BC Retry                                             | 4-26 |

| Bit 15 - Bus Select                                                 | 4-26 |

| BUFPTR                                                              | 4-26 |

| LINK                                                                | 4-26 |

| Controlling BC Operation - BCIPTR, BCCPTR, BCLPTR                   | 4-27 |

| Status Word Mask - BCSMSK                                           | 4-27 |

| BC Retries - BRTCNT,BRTBUS,BRTCMD,BRTRTC                            | 4-27 |

| Mode Codes                                                          | 4-28 |

|                                                                     |      |

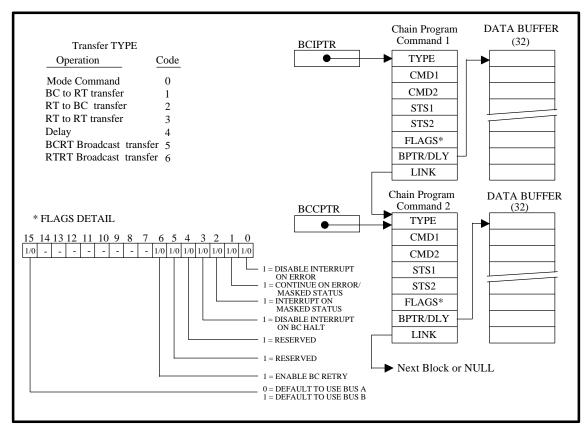

| Remote Terminal Simulation                                          | 4-29 |

| Status Word Table - Enabling RT Simulation                          | 4-30 |

| Status Word Response Bits                                           | 4-31 |

| Bit 0 - Terminal Flag Bit                                           | 4-31 |

| Bit 1 - Bus Control Accept Bit                                      | 4-31 |

| Bit 2 - Subsystem Flag Bit                                          | 4-31 |

| Bit 3 - Busy                                                        | 4-31 |

| Bit 4 - Broadcast Command Received Bit                              | 4-32 |

| Bit 8 - Service Request Bit                                         | 4-32 |

| Bit 9 - Instrumentation Bit                                         | 4-32 |

| Bit 10 -Message Error Bit                                           | 4-32 |

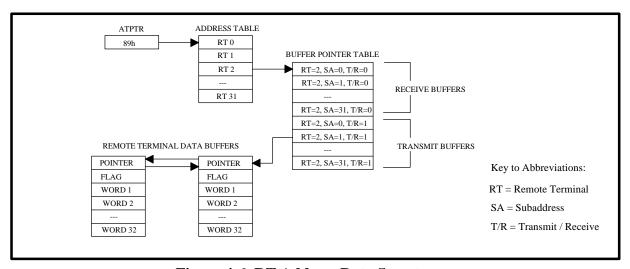

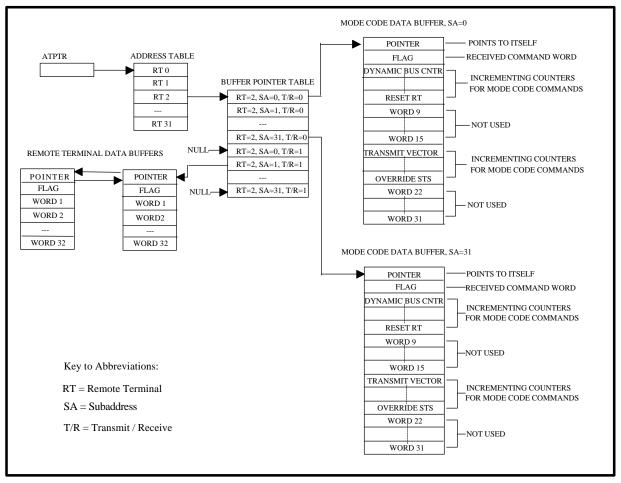

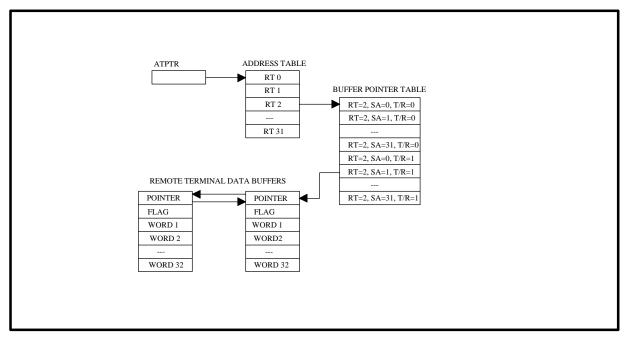

| RT Address Data Structures                                          | 4-32 |

| Defining Data Word Buffers                                          | 4-32 |

| Address Table                                                       | 4-33 |

| Buffer Pointer Table                                                | 4-34 |

| Data Buffer Format                                                  | 4-34 |

| Broadcast Considerations                                            | 4-34 |

| Minimum Programming Requirements for the RT Address Data Structures | 4-35 |

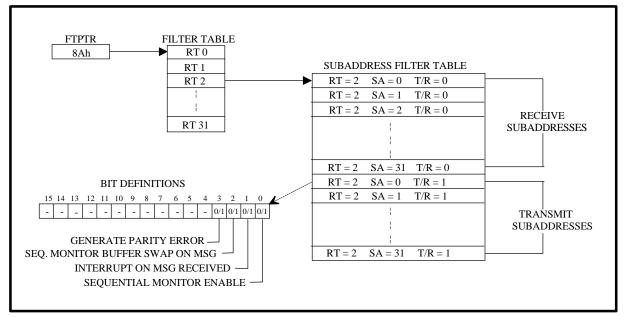

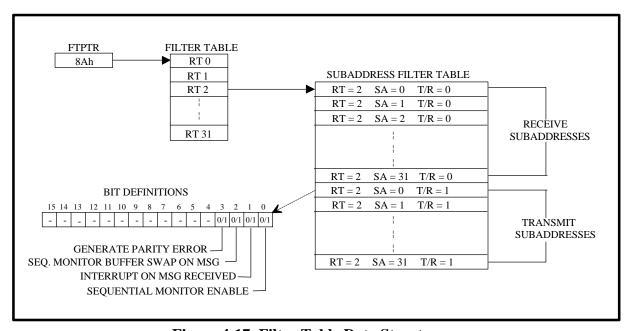

| Filter Table                                                        | 4-35 |

| Bit 0 - Sequential Monitor Enable                                   |      |

| Bit 1 - Interrupt on Message Received                               | 4-36 |

# Full Function Programmer's Reference TABLE OF CONTENTS

| Bit 2 - Sequential Monitor Buffer Swap on Message       | 4-36 |

|---------------------------------------------------------|------|

| Bit 3 - Generate Parity Error                           | 4-36 |

| Minimum Programming Requirements for the Filter Table   | 4-36 |

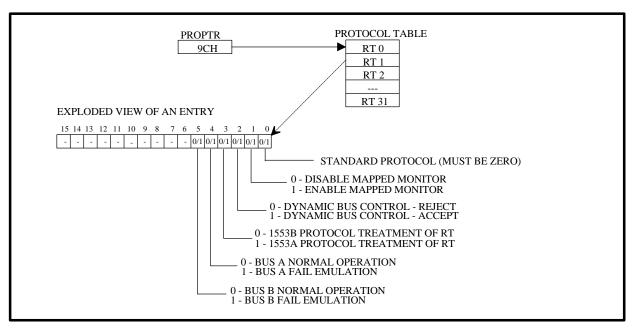

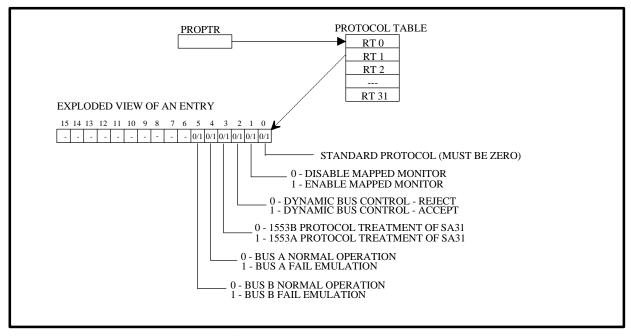

| Protocol Table                                          | 4-36 |

| Bit 0 - Standard Protocol                               | 4-37 |

| Bit 1 - Mapped Monitor Enable                           | 4-37 |

| Bit 2 - Dynamic Bus Control                             | 4-37 |

| Bit 3 - Treatment of RT                                 | 4-38 |

| 1553A Protocol                                          | 4-38 |

| Bit 4 - Bus A Operation                                 | 4-38 |

| Bit 5 - Bus B Operation                                 | 4-38 |

| Minimum Programming Requirements for the Protocol Table | 4-38 |

| RT Mode Code Simulation                                 | 4-38 |

| Mode Code Data Structures Required for ABI Operations   | 4-40 |

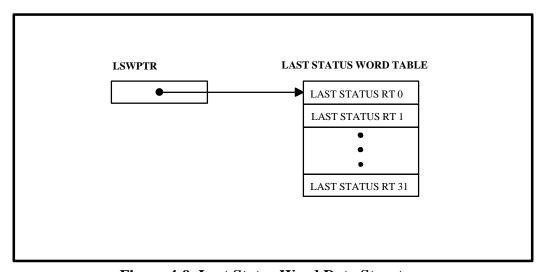

| Last Status Word Data Structure                         | 4-40 |

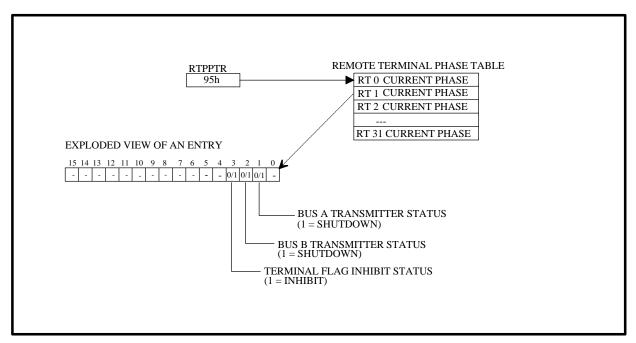

| RT Phase Data Structure                                 | 4-41 |

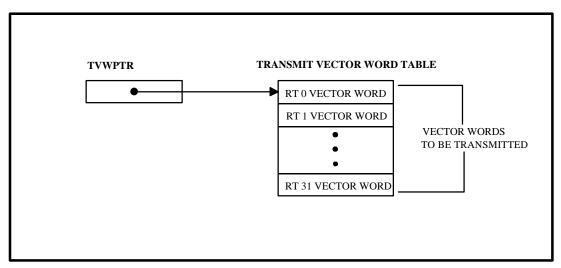

| Transmit Vector Word Data Structure                     | 4-42 |

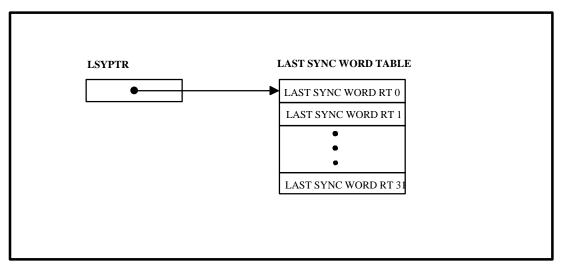

| Last Sync Word Data Structure                           | 4-43 |

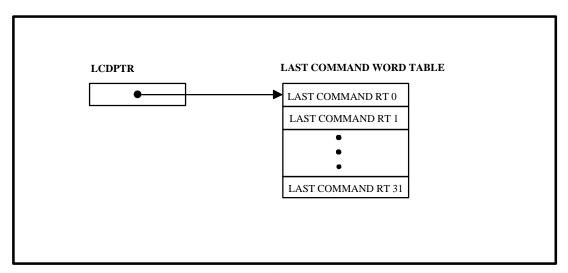

| Last Command Data Structure                             | 4-44 |

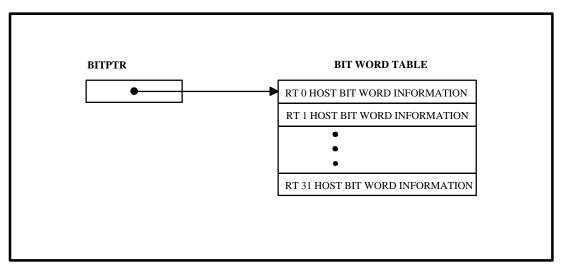

| Bit Word Data Structure                                 | 4-45 |

| Optional Mode Code Data Structures                      | 4-45 |

| Filter Table                                            | 4-45 |

| RT Address Data Structures                              | 4-45 |

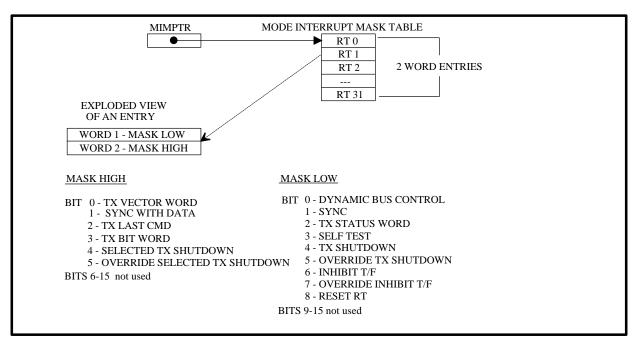

| Mode Command Interrupt Table                            | 4-45 |

| RT Address Mode Code Data Buffer Format                 | 4-46 |

| Mode Interrupt Mask Table                               | 4-47 |

| Variable Intermessage and Status Response Gap Times     | 4-48 |

| 1553 Bus Monitoring                                     | 4-49 |

| Sequential Monitoring                                   |      |

| Filter Table                                            | 4-50 |

| Sequential Monitor Buffers                              | 4-50 |

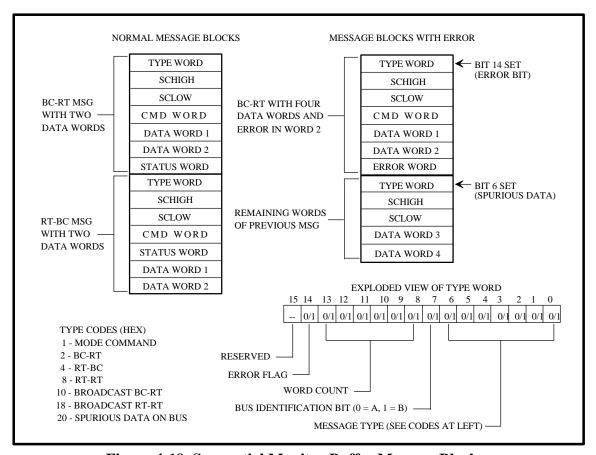

| Bits 0-6 - Message Type                                 | 4-52 |

| Bit 7 - Bus Identification Bit                          |      |

| Bits 8-13 - Word Count                                  | 4-53 |

|                                                         |      |

# Full Function Programmer's Reference TABLE OF CONTENTS

| Bit 14 - Error Flag                                             | 4-53 |

|-----------------------------------------------------------------|------|

| Minimum Programming Requirements for Sequential Monitor Buffers | 4-53 |

| Buffer Swap Detection                                           | 4-54 |

| Forcing Buffer Swaps                                            | 4-54 |

| Map Monitoring                                                  | 4-54 |

| Map Monitoring Data Structures                                  | 4-55 |

|                                                                 |      |

| Interrupts                                                      | 4-57 |

| Interrupt Types                                                 | 4-57 |

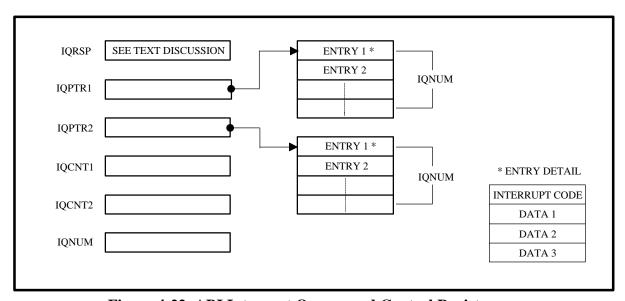

| Interrupt Queue Data Structures and Control Registers           | 4-59 |

| Minimum Programming Requirements for Interrupt Queues           | 4-60 |

| Hardware Interrupt Service Procedure                            | 4-62 |

| Software Polling Interrupt Service Procedure                    | 1 62 |

# Full Function Programmer's Reference TABLE OF FIGURES AND TABLES

| Figure 4-1 ABI Architecture                                | -2         |

|------------------------------------------------------------|------------|

| Figure 4-2 ABI Memory Organization                         | -4         |

| Table 4-1 ABI Control Registers                            | -6         |

| Figure 4-3 Control Status Register Bits                    | 11         |

| Table 4-2 Control Status Register Bit Definitions          | 11         |

| Table 4-3 Variable Voltage DAC Register                    | 15         |

| Table 4-4 ABI Error Table                                  | 16         |

| Table 4-5 Microcode Program Identification                 | 19         |

| Figure 4-4 BC Control Structures                           | 24         |

| Table 4-6 BC Type Codes                                    | 24         |

| Figure 4-5 RT Status Word Table (SWTPTR)                   | 30         |

| Figure 4-6 RT Address Data Structures                      | 33         |

| Figure 4-7 Filter Table Data Structures                    | 35         |

| Figure 4-8 Protocol Table                                  | 37         |

| Table 4-7 ABI Mode Code Operations                         | 39         |

| Figure 4-9 Last Status Word Data Structure                 | <b>4</b> 0 |

| Figure 4-10 RT Phase Table Data Structure                  | 41         |

| Figure 4-11 Transmit Vector Word Table                     | <b>1</b> 2 |

| Figure 4-12 Last Sync Word Table                           | 43         |

| Figure 4-13 Last Command Word Table                        | 14         |

| Figure 4-14 Bit Word Table                                 | 45         |

| Figure 4-15 RT Address Mode Code Data Buffer 4-4           | 46         |

| Figure 4-16 Mode Interrupt Mask Table                      | 17         |

| Figure 4-17 Filter Table Data Structures                   | 50         |

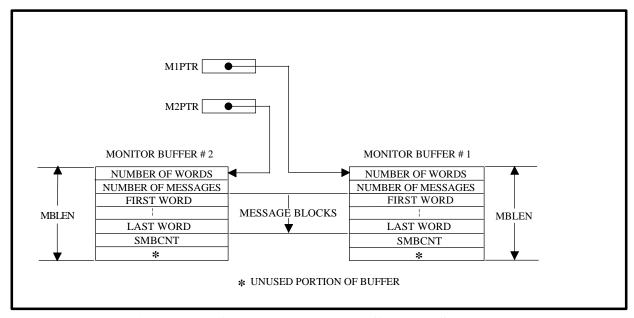

| Figure 4-18 Sequential Monitor Buffer Data Structures 4-5  | 51         |

| Figure 4-19 Sequential Monitor Buffer Message Blocks       | 52         |

| Figure 4-20 RT Address Data Structures                     | 55         |

| Figure 4-21 Protocol Table                                 | 55         |

| Table 4-8 ABI Interrupt Types                              | 58         |

| Figure 4-22 ABI Interrupt Queues and Control Registers 4-5 | 59         |

| Table 4-9 Interrupt Word Descriptions                      | 51         |

| Table 4-10 Hardware Interrupt Service Procedure 4-6        | 52         |

| Table 4-11 Software Polling Interrupt Service Procedure    | 53         |

# **FULL FUNCTION PROGRAMMER'S REFERENCE**

The Advanced Bus Interface (ABI) module provides the host computer with a real-time MIL-STD-1553 interface. The ABI is capable of simultaneous and independent Bus Controller (BC) and 31 Remote Terminal (RT) simulation as well as Map and Sequential Monitoring operations. This section of the manual details the operations of the ABI and contains the following subsections:

- Introduction / ABI Operations Overview

- Microcode Initialization

- BC Simulation

- RT Simulation

- Bus Monitoring

- Interrupts

NOTE: This manual section assumes the user has previous knowledge of MIL-STD-1553 operations.

The "ABI Operations Overview" subsection discusses ABI memory organization and microcode program operations. The "Microcode Initialization" subsection explains the required steps in initializing an ABI. The three subsections following Microcode Initialization detail ABI configuration for Bus Controller, Remote Terminal and Monitor operations. The "Interrupts" subsection explains ABI interrupt capabilities and the recommended servicing procedures for hardware and software polled interrupts.